## **Features**

- Wide Voltage Operation

- VCC = 1.8V to 5.5V

- Operating Ambient Temperature:  $-40^{\circ}$ C to  $+85^{\circ}$ C

- Internally Organized:

- HG24C02, 256 X 8 (2K bits)

- HG24C04, 512 X 8 (4K bits)

- HG24C08, 1024 X 8 (8K bits)

- HG24C16, 2048 X 8 (16K bits)

- Two-wire Serial Interface

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- Bidirectional Data Transfer Protocol

- 1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) Compatibility

- Write Protect Pin for Hardware Data Protection

- 8-byte Page (2K), 16-byte Page (4K, 8K, 16K) Write Modes

- Partial Page Writes Allowed

- Self-timed Write Cycle (5 ms max)

- High-reliability

- Endurance: 1 Million Write Cycles

- Data Retention: 100 Years

- Die Sales: Wafer Form, Waffle Pack

#### ORDERING INFORMATION

| DEVICE       | Package Type | MARKING | Packing | Packing Qty |

|--------------|--------------|---------|---------|-------------|

| HG24C02N     | DIP8         | 24C02   | TUBE    | 2000/box    |

| HG24C04N     | DIP8         | 24C04   | TUBE    | 2000/box    |

| HG24C08N     | DIP8         | 24C08   | TUBE    | 2000/box    |

| HG24C16N     | DIP8         | 24C16   | TUBE    | 2000/box    |

| HG24C02M/TR  | SOP8         | 24C02   | REEL    | 2500/reel   |

| HG24C04M/TR  | SOP8         | 24C04   | REEL    | 2500/reel   |

| HG24C08M/TR  | SOP8         | 24C08   | REEL    | 2500/reel   |

| HG24C16M/TR  | SOP8         | 24C16   | REEL    | 2500/reel   |

| HG24C02MT/TR | TSSOP8       | 24C02   | REEL    | 2500/reel   |

| HG24C04MT/TR | TSSOP8       | 24C04   | REEL    | 2500/reel   |

| HG24C08MT/TR | TSSOP8       | 24C08   | REEL    | 2500/reel   |

| HG24C16MT/TR | TSSOP8       | 24C16   | REEL    | 2500/reel   |

## **General Description**

The HG24C02 / HG 24C04 / HG24C08 / HG24C16 provides 2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 256/512/1024/2048 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operations are essential. The HG24C02 / HG24C04 / HG24C08 / HG24C16 is available in space-saving 8-lead DIP, 8-lead SOP, and 8-lead TSSOP packages and is accessed via a two-wire serial interface.

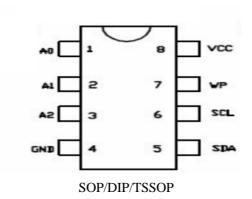

# **Pin Configuration**

# **Pin Descriptions**

Table 1: Pin Configuration

| Pin Designation | Type             | Name and Functions |

|-----------------|------------------|--------------------|

| A0 - A2         | I                | Address Inputs     |

| SDA             | I/O & Open-drain | Serial Data        |

| SCL             | I                | Serial Clock Input |

| WP              | I                | Write Protect      |

| GND             | P                | Ground             |

| VCC             | P                | Power Supply       |

| NC              | NC               | No Connect         |

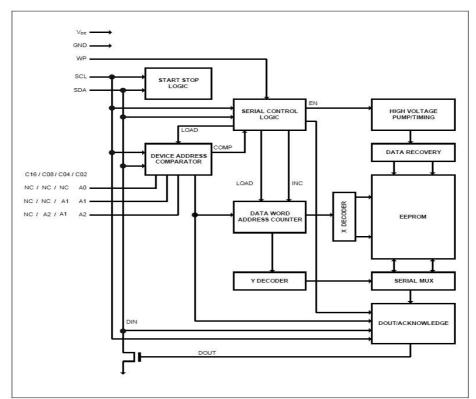

# **Block Diagram**

# **Pin Descriptions**

**DEVICE/PAGE ADDRESSES** (**A2, A1 and A0**): The A2, A1 and A0 pins are device address inputs that are hard wired for the HG24C02. Eight 2K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section).

The HG24C04 uses the A2 and A1 inputs for hard wire addressing and a total of four 4K devices may be addressed on a single bus system. The A0 pin is a no connect and can be connected to ground. The HG24C08 only uses the A2 input for hardwire addressing and a total of two 8K devices may be addressed on a single bus system. The A0 and A1 pins are no connects and can be connected to ground.

The HG24C16 does not use the device address pins, which limits the number of devices on a single bus to one. The A0, A1 and A2 pins are no connects and can be connected to ground.

**SERIAL DATA (SDA):** The SDA pin is bi-directional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open- collector devices.

**SERIAL CLOCK (SCL):** The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.

**WRITE PROTECT (WP):** The HG24C02 /HG24C04 /HG24C08 /HG24C16 has a Write Protect pin that provides hardware data protection. The Write Protect pin allows normal read/write operations when connected to ground (GND). When the Write Protect pin is connected to VCC, the write protection feature is enabled and operates as shown in the following Table 2.

Table 2: Write Protect

| WP Pin Status   | Part of the Array Protected  |                 |                 |                  |  |  |  |  |

|-----------------|------------------------------|-----------------|-----------------|------------------|--|--|--|--|

| WI I III Status | HG24C02                      | HG24C04         | HG24C08         | HG24C16          |  |  |  |  |

| At VCC          | Full (2K) Array              | Full (4K) Array | Full (8K) Array | Full (16K) Array |  |  |  |  |

| At GND          | Normal Read/Write Operations |                 |                 |                  |  |  |  |  |

# **Memory Organization**

**HG24C02**, **2K SERIAL EEPROM:** Internally organized with 32 pages of 8 bytes each, the 2K requires an 8-bit data word address for random word addressing.

**HG24C04**, **4K SERIAL EEPROM:** Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit data word address for random word addressing.

**HG24C08**, **8K SERIAL EEPROM:** Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address for random word addressing.

**HG24C16**, **16K SERIAL EEPROM:** Internally organized with 128 pages of 16 bytes each, the 16K requires an 11-bit data word address for random word addressing.

# **Device Operation**

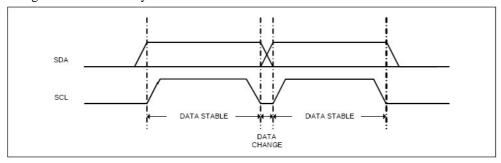

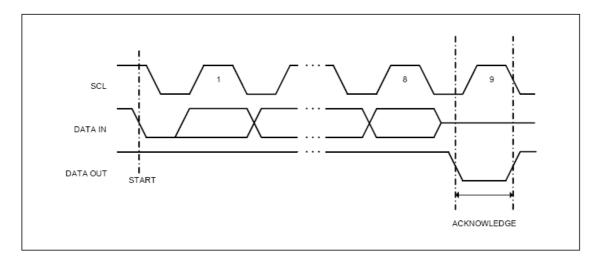

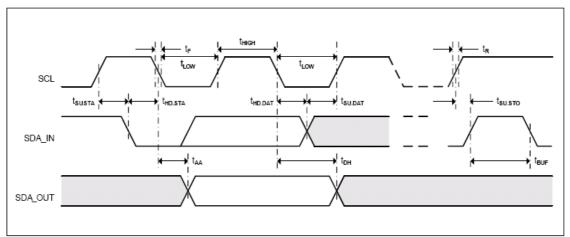

**CLOCK and DATA TRANSITIONS:** The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see to Figure 1 on page 5). Data changes during SCL high periods will indicate a start or stop condition as defined below.

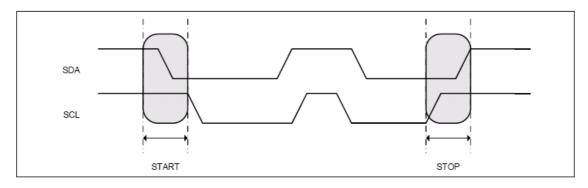

START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which

must precede any other command (see to Figure 2 on page 5).

**STOP CONDITION:** A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 2 on page 5).

**ACKNOWLEDGE:** All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a "0" to acknowledge that it has received each word. This happens during the ninth clock cycle.

**STANDBY MODE:** The HG24C02 / HG24C04 / HG24C08 / HG24C16 features a low-power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the STOP bit and the completion of any internal operations.

**MEMORY RESET:** After an interruption in protocol, power loss or system reset, any two-wire part can be reset by following these steps:

- 1. Clock up to 9 cycles.

- 2. Look for SDA high in each cycle while SCL is high.

- 3. Create a start condition.

#### • Figure 1: Data Validity

#### I Figure 2: Start and Stop Definition

#### • Figure 3: Output Acknowledge

## **Device Addressing**

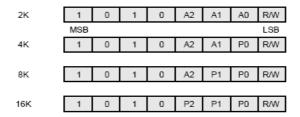

The 2K, 4K, 8K and 16K EEPROM devices all require an 8-bit device address word following a start condition to enable the chip for a read or write operation (see to Figure 4 on page 8).

The device address word consists of a mandatory "1", "0" sequence for the first four most significant bits as shown. This is common to all the Serial EEPROM devices.

The next 3 bits are the A2, A1 and A0 device address bits for the 2K EEPROM. These 3 bits must compare to their corresponding hardwired input pins.

The 4K EEPROM only uses the A2 and A1 device address bits with the third bit being a memory page address bit. The two device address bits must compare to their corresponding hardwired input pins. The A0 pin is no connect.

The 8K EEPROM only uses the A2 device address bit with the next 2 bits being for memory page addressing. The A2 bit must compare to its corresponding hard-wired input pin. The A1 and A0 pins are no connect.

The 16K does not use any device address bits but instead the 3 bits are used for memory page addressing. These page addressing bits on the 4K, 8K and 16K devices should be considered the most significant bits of the data word address which follows. The A0, A1 and A2 pins are no connect. The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.

Upon a compare of the device address, the EEPROM will output a "0". If a compare is not made, the chip will return to a standby state.

# **Write Operations**

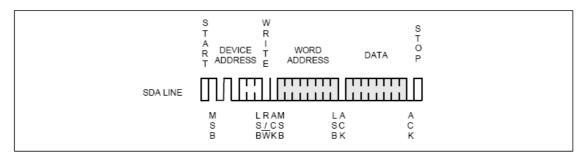

**BYTE WRITE:** A write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a "0"

and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a "0" and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally timed write cycle, twr, to the

nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 5 on page 7).

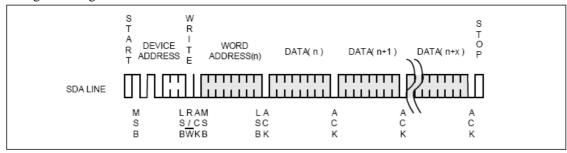

**PAGE WRITE:** The 2K EEPROM is capable of an 8-byte page write, and the 4K, 8K and 16K devices are capable of 16-byte page writes.

A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to seven (2K) or fifteen (4K, 8K, 16K) more data words. The EEPROM will respond with a "0" after each data word received. The microcontroller must terminate the page write sequence with a stop condition (see Figure 6 on page 8). The data word address lower three (2K) or four (4K, 8K, 16K) bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than eight (2K) or sixteen (4K, 8K, 16K) data words are transmitted to the EEPROM, the data word address will "roll over" and previous data will be overwritten.

**ACKNOWLEDGE POLLING:** Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a "0", allowing the read or write sequence to continue.

# **Read Operations**

Read operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to "1". There are three read operations: current address read, random address read and sequential read.

**CURRENT ADDRESS READ:** The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address "roll over" during read is from the last byte of the last memory page to the first byte of the first page. The address "roll over" during write is from the last byte of the current page to the first byte of the same page.

Once the device address with the read/write select bit set to "1" is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input "0" but does generate a following stop condition (see Figure 7 on page 8).

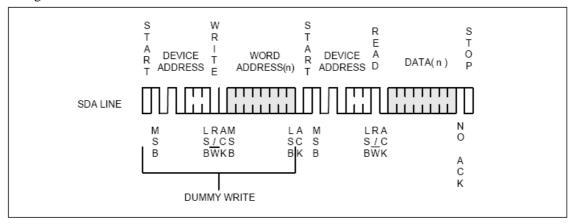

**RANDOM READ:** A random read requires a "dummy" byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a "0" but does generate a following stop condition (see Figure 8 on page 9).

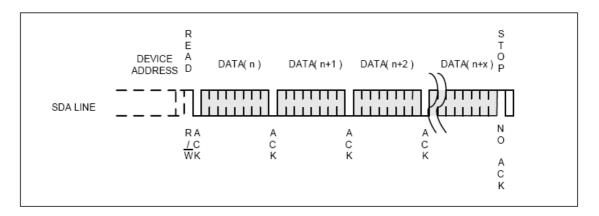

**SEQUENTIAL READ:** Sequential reads are initiated by either a current address read or a random

address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will "roll over" and the sequential read will continue. The sequential read operation is terminated when the microcontroller does not respond with a "0" but does generate a following stop

condition (see Figure 9 on page 9).

### I Figure 4: Device Address

### I Figure 5: Byte Write

### I Figure 6: Page Write

### I Figure 7: Current Address Read

### I Figure 8: Random Read

### I Figure 9: Sequential Read

# **Electrical Characteristics**

| I Absolute Maximum Stress Ratings |               |         |  |  |  |  |

|-----------------------------------|---------------|---------|--|--|--|--|

| DC Supply Voltage                 | 0.3V to +6.5V | Input / |  |  |  |  |

| Operating Ambient Temperature     | 40℃ to +85℃   | Storag  |  |  |  |  |

Input / Output Voltage . . . . . . GND-0.3V to Vcc+0.3V Storage Temperature . . . . . . . -65  $^{\circ}$ C to +150  $^{\circ}$ C

#### I Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

## **DC Electrical Characteristics**

Applicable over recommended operating range from:  $TA = -40^{\circ}C$  to  $+85^{\circ}C$ , VCC = +1.8V to +5.5V (unless otherwise noted)

| Parameter                 | Symbol           | Min.             | Typ. | Max.      | Unit | Condition       |

|---------------------------|------------------|------------------|------|-----------|------|-----------------|

| Supply Voltage            | Vcc              | 1.8              | -    | 5.5       | V    |                 |

| Supply Current Vcc=5.0V   | Icc1             | ı                | 0.4  | 1.0       | mA   | Read @100KHz    |

| Supply Current Vcc=5.0V   | Icc2             | ı                | 2.0  | 3.0       | mA   | Write @100KHz   |

| Standby Current           | Isb              | ı                | -    | 2.0       | uA   | Vin=Vcc or GND  |

| Input Leakage Current     | Ili              | -                | -    | 3.0       | uA   | Vin=Vcc or GND  |

| Output Leakage Current    | Iro              | ı                | 0.05 | 3.0       | uA   | Vout=Vcc or GND |

| Input Low Level           | VIL              | -0.6             | -    | Vcc×0.3   | V    |                 |

| Input High Level          | VIH              | $Vcc \times 0.7$ | -    | Vcc + 0.5 | V    |                 |

| Output Low Level Vcc=5.0V | V <sub>OL3</sub> | -                | -    | 0.4       | V    | Iol=3.0mA       |

| Output Low Level Vcc=3.0V | $V_{OL2}$        | -                | -    | 0.4       | V    | Iot=2.1mA       |

| Output Low Level Vcc=1.8V | Voli             | -                | -    | 0.2       | V    | Iot=0.15mA      |

# Pin Capacitance

Applicable over recommended operating range from TA =  $25^{\circ}$ C, f = 1.0 MHz, VCC = +1.8V

| Parameter                           | Symbol | Min. | Typ. | Max. | Unit | Condition     |

|-------------------------------------|--------|------|------|------|------|---------------|

| Input/Output Capacitance (SDA)      | Сио    | -    | -    | 8    | pF   | $V_{VO} = 0V$ |

| Input Capacitance (A0, A1, A2, SCL) | Cin    | -    | ı    | 6    | pF   | $V_{IN} = 0V$ |

## **AC Electrical Characteristics**

Applicable over recommended operating range from  $TA = -40\,^{\circ}\text{C}$  to  $+85\,^{\circ}\text{C}$ ,  $VCC = +1.8\,\text{V}$  to  $+5.5\,\text{V}$ ,  $CL = 1\,\text{TTL}$  Gate and  $100\,\text{pF}$  (unless otherwise noted)

| Parameter                                                     | Symbol                      |      | 1.8-volt |      |      | 5.0-volt |      | Units        |

|---------------------------------------------------------------|-----------------------------|------|----------|------|------|----------|------|--------------|

| Parameter                                                     | Symbol                      | Min. | Тур.     | Max. | Min. | Тур.     | Max. | Ullis        |

| Clock Frequency, SCL                                          | $\mathbf{f}_{\mathtt{SCL}}$ | -    | -        | 400  | -    | -        | 1000 | KHz          |

| Clock Pulse Width Low                                         | tlow                        | 1.2  | -        | -    | 0.6  | -        | -    | us           |

| Clock Pulse Width High                                        | tніgн                       | 0.6  | -        | -    | 0.4  | -        | -    | us           |

| Noise Suppression Time                                        | <b>t</b> ı                  | -    | -        | 50   | -    | -        | 40   | us           |

| Clock Low to Data Out Valid                                   | <b>t</b> AA                 | 0.05 | -        | 0.9  | 0.05 | -        | 0.55 | us           |

| Time the bus must be free before a new transmission can start | <b>t</b> BUF                | 1.2  | -        | -    | 0.5  | -        | -    | us           |

| Start Hold Time                                               | thd.sta                     | 0.6  | -        | -    | 0.25 | -        | -    | us           |

| Start Setup Time                                              | tsu.sta                     | 0.6  | -        | -    | 0.25 | -        | -    | us           |

| Data In Hold Time                                             | thd.dat                     | 0    | -        | -    | 0    | -        | -    | us           |

| Data In Setup Time                                            | <b>t</b> su.dat             | 100  | -        | -    | 100  | -        | -    | ns           |

| Inputs Rise Time(1)                                           | <b>t</b> r                  | -    | -        | 0.3  | -    | -        | 0.3  | us           |

| Inputs Fall Time(1)                                           | <b>t</b> F                  | -    | -        | 300  | -    | -        | 100  | ns           |

| Stop Setup Time                                               | tsu.sto                     | 0.6  | -        | -    | 0.25 | -        | -    | us           |

| Data Out Hold Time                                            | <b>t</b> dh                 | 50   | -        | -    | 50   | -        | -    | ns           |

| Write Cycle Time                                              | twr                         | -    | -        | 5    | -    | -        | 5    | ms           |

| 5.0V, 25℃, Byte Mode                                          | Endurance                   | 1M   | -        | -    | -    | -        | -    | Write Cycles |

#### Note

1. This parameter is characterized and is not 100% tested.

2. AC measurement conditions: RL (connects to VCC):  $1.3 \text{ k}\Omega$  (2.5V, 5V),  $10 \text{ k}\Omega$  (1.8V)

Input pulse voltages: 0.3 VCC to 0.7 VCC

Input rise and fall time: ≤50 ns

Input and output timing reference voltages: 0.5 VCC

The value of RL should be concerned according to the actual loading on the user's system.

# **Bus Timing**

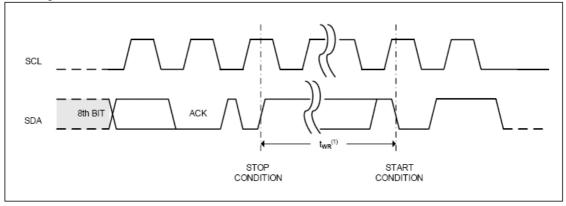

Figure 10: SCL: Serial Clock, SDA: Serial Data I/O

# **Write Cycle Timing**

#### Note

1. The write cycle time twR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.

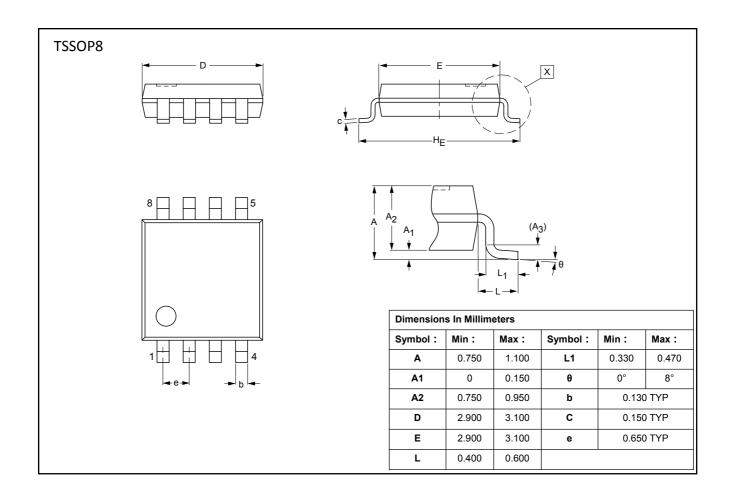

## **PACKAGE**

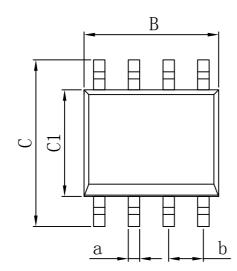

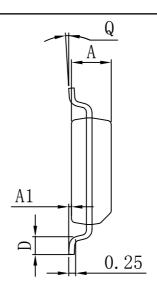

## SOP8

| UNIT: mm |       |       |       |      |       |       |       |

|----------|-------|-------|-------|------|-------|-------|-------|

| DIM.     | MIN   | TYP   | MAX   | DIM. | MIN   | TYP   | MAX   |

| A        | 4.520 | 4.570 | 4.620 | a    | 0.400 | 0.420 | 0.440 |

| A1       | 0.100 | _     | 0.250 | b    | 1.260 | 1.270 | 1.280 |

| В        | 4.800 | 4.920 | 5.100 | Q    | 0°    | -     | 8°    |

| С        | 5.800 | 6.100 | 6.250 |      |       |       |       |

| C1       | 3.800 | 3.900 | 4.000 |      |       |       |       |

| D        | 0.400 | -     | 0.950 |      |       |       |       |

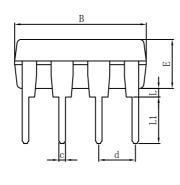

## DIP8

| UNIT: mm |        |       |       |      |       |       |       |

|----------|--------|-------|-------|------|-------|-------|-------|

| DIM.     | MIN    | TYP   | MAX   | DIM. | MIN   | TYP   | MAX   |

| A        | 6.100  | 6.300 | 6.680 | a    | 1.504 | 1.524 | 1.544 |

| В        | 9.000  | 9.200 | 9.500 | b    | -     | 0.889 | -     |

| D        | 8.400  | 8.700 | 9.000 | С    | 0.437 | 0.457 | 0.477 |

| D1       | 7.42   | 7.62  | 7.82  | d    | 2.530 | 2.540 | 2.550 |

| Е        | 3. 100 | 3.300 | 3.550 | L    | 0.500 | -     | 0.700 |

|          |        |       |       | L1   | 3.000 | 3.200 | 3.600 |

## Important statement:

Huaguan Semiconductor Co,Ltd. reserves the right to change the products and services provided without notice. Customers should obtain the latest relevant information before ordering, and verify the timeliness and accuracy of this information.

Customers are responsible for complying with safety standards and taking safety measures when using our products for system design and machine manufacturing to avoid potential risks that may result in personal injury or property damage.

Our products are not licensed for applications in life support, military, aerospace, etc., so we do not bear the consequences of the application of these products in these fields.

Our documentation is only permitted to be copied without any tampering with the content, so we do not accept any responsibility or liability for the altered documents.