# **RFSA3613**

5MHz to 6000MHz, Digital Step Attenuator

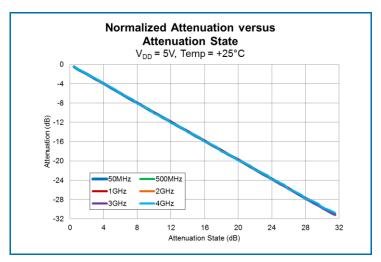

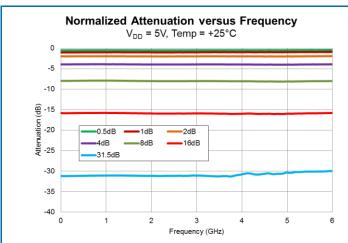

The RFMD's RFSA3613 is a 6-bit digital step attenuator (DSA) that features high linearity over the entire 31.5dB gain control range with 0.5dB steps. The RFSA3613 uses serial control interface. The RFSA3613 has a low insertion loss of 1.4dB at 2GHz. Patent pending circuit architecture provides overshoot-free transient switching performance. External address pins allow up to eight DSAs to be controlled on a single bus. The RFSA3613 is available in a 3mm x 3mm QFN package.

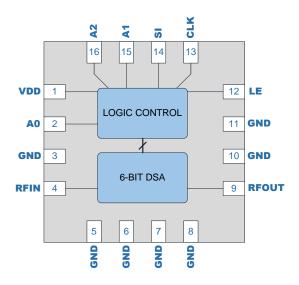

Functional Block Diagram

# **Ordering Information**

| RFSA3613SQ      | Sample bag with 25 pieces                    |

|-----------------|----------------------------------------------|

| RFSA3613SR      | 7" Reel with 100 pieces                      |

| RFSA3613TR7     | 7" Reel with 2500 pieces                     |

| RFSA3613PCK-410 | 5MHz to 6000MHz PCBA with 5-piece sample bag |

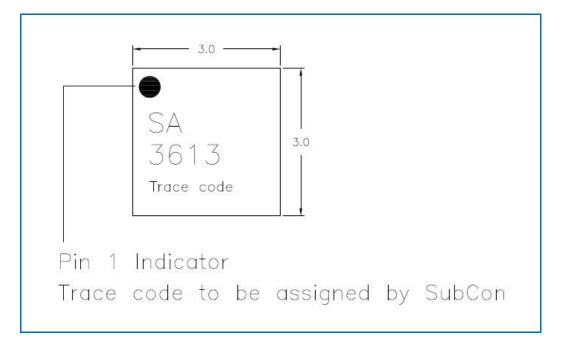

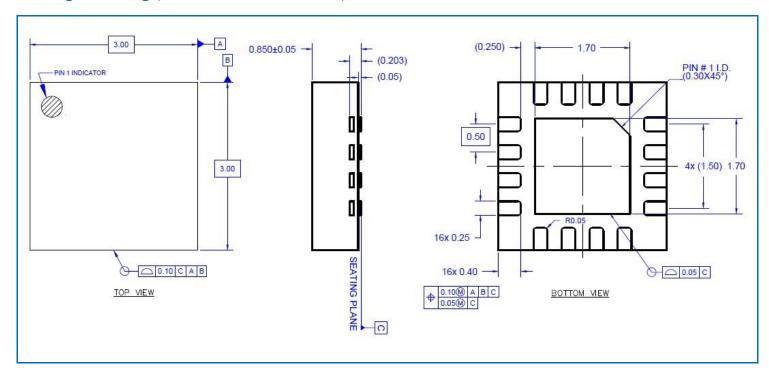

Package: QFN, 16-pin, 3.0mm x 3.0mm x 0.85mm

#### **Features**

- 6-Bit, 31.5dB Range, 0.5dB Step

- Patent Pending Circuit Architecture

- Overshoot-free Transient Switching Performance

- Frequency Range 5MHz to 6000MHz

- High Linearity, IIP3 >55dBm

- Serial Control Interface

- Fast Switching Speed, <120nsec Typical

- Serial Addressable Supports Up to Eight Addresses

- Single Supply 3V to 5V Operation

- RF Pins Have No DC Voltage, Can be DC Grounded Externally

- Power-up Default Setting Is Maximum Attenuation

#### **Applications**

- 2G through 4G Base Stations

- Point-to-Point

- WiFi

- Test Equipment

#### **Absolute Maximum Ratings**

| Parameter                                                                                    | Rating                  | Unit |

|----------------------------------------------------------------------------------------------|-------------------------|------|

| Supply Voltage (V <sub>DD</sub> )                                                            | -0.5 to +6.0            | V    |

| All Other DC and Logic Pins (Supply Voltage Must Be Applied Prior to Any Other Pin Voltages) | -0.5 to V <sub>DD</sub> | V    |

| Maximum Input Power at RFIN Pin at 85°C Case Temperature                                     | +30                     | dBm  |

| Maximum Input Power at RFOUT Pin at 85°C Case Temperature                                    | +27                     | dBm  |

| Storage Temperature Range                                                                    | -40 to +150             | °C   |

| ESD Rating - Human Body Model (HBM)                                                          | 1000                    | V    |

| Moisture Sensitivity Level                                                                   | MSL1                    |      |

Caution! ESD sensitive device.

RFMD Green: RoHS status based on EU Directive 2011/65/EU (at time of this document revision), halogen free per IEC 61249-2-21, < 1000ppm each of antimony trioxide in polymeric materials and red phosphorus as a flame retardant, and <2% antimony in solder.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

#### **Recommended Operating Condition**

| Parameter                                                                | Specification |     |      |      |  |

|--------------------------------------------------------------------------|---------------|-----|------|------|--|

| raiailietei                                                              | Min           | Тур | Max  | Unit |  |

| Operating Temperature Range (RF Input Power Handling Derates Above 85°C) | -40           |     | +105 | °C   |  |

| Operating Junction Temperature                                           |               |     | 125  | °C   |  |

| Supply Voltage                                                           | 2.7           |     | 5.5  | V    |  |

#### **Nominal Operating Parameters**

| Dayamatar                   | Specification |          |      | 1120 | Condition                                                                            |  |  |

|-----------------------------|---------------|----------|------|------|--------------------------------------------------------------------------------------|--|--|

| Parameter                   | Min           | Тур      | Max  | Unit | Condition                                                                            |  |  |

| General Performance         |               |          |      |      |                                                                                      |  |  |

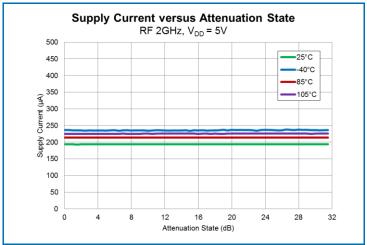

| Supply Current              |               | 180      |      | μΑ   | Steady state operation, current draw during attenuation state transitions is higher. |  |  |

| Thermal Resistance          |               | 55       |      | °C/W | At maximum attenuation state with RF power applied to the RFIN pin                   |  |  |

| RF Input Power at RFIN Pin  |               |          | 27   | dBm  | Continuous anastina at 1000 anna tamananatura                                        |  |  |

| RF Input Power at RFOUT Pin |               |          | 20   | dBm  | Continuous operation at +85°C case temperature                                       |  |  |

| RF Performance              |               |          |      |      |                                                                                      |  |  |

| Frequency Range             | 5             |          | 6000 | MHz  |                                                                                      |  |  |

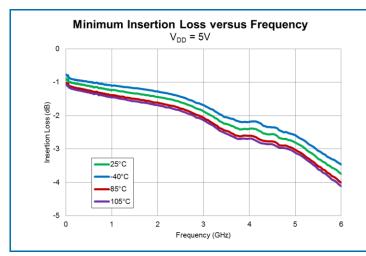

| Insertion Loss              |               | 1.4      |      | dB   | 2000MHz, 0dB attenuation                                                             |  |  |

| Attenuation Range           |               | 31.5     |      | dB   | 0.5dB step size                                                                      |  |  |

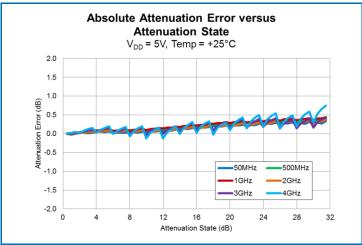

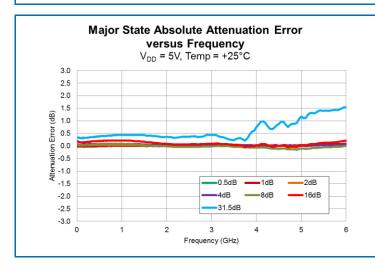

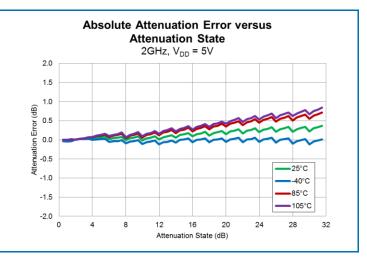

| Absolute Attenuation Error  | ±             | (0.2 + 4 | %)   | dB   | 2000MHz                                                                              |  |  |

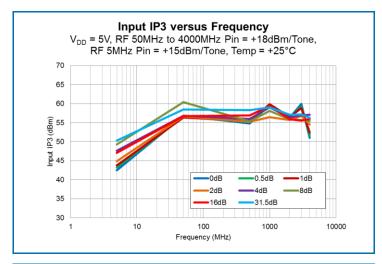

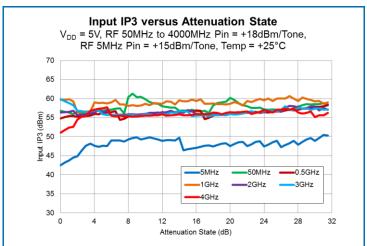

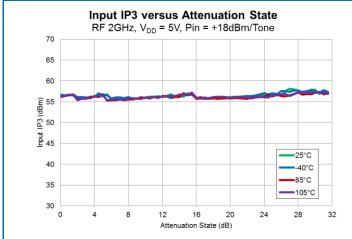

| Input IP3                   |               | 55       |      | dBm  |                                                                                      |  |  |

| Input P0.1dB                |               | 30       |      | dBm  |                                                                                      |  |  |

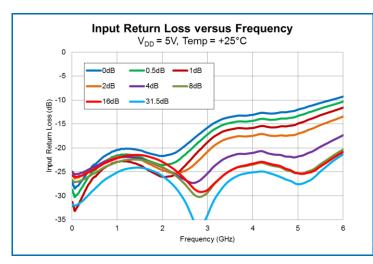

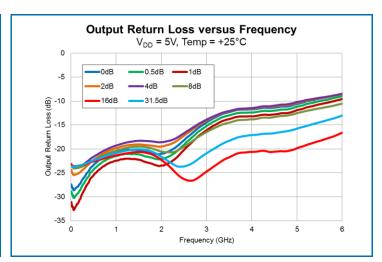

| Return Loss                 |               | 15       |      | dB   |                                                                                      |  |  |

| Input and Output Impedance  |               | 50       |      | Ω    |                                                                                      |  |  |

| Parameter                   | Specification |     |           | Unit | Condition                 |  |  |

|-----------------------------|---------------|-----|-----------|------|---------------------------|--|--|

| raianietei                  | Min Typ Max   |     | Condition |      |                           |  |  |

| General Performance         |               |     |           |      |                           |  |  |

| Switching Speed             |               | 120 |           | nsec | 50% control to 10%/90% RF |  |  |

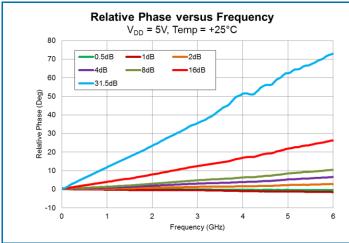

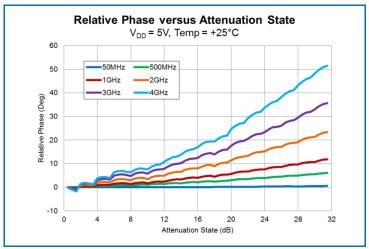

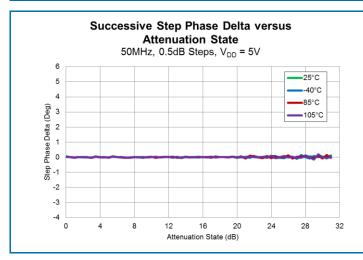

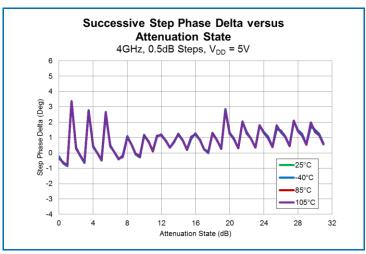

| Successive Step Phase Delta |               | 2   |           | Deg  | 2000MHz                   |  |  |

| Control                     |               |     |           |      |                           |  |  |

| Digital Logic Low           |               |     | 0.63      | V    |                           |  |  |

| Digital Logic High          | 1.17          |     |           | V    |                           |  |  |

Note: Typical performance at these conditions: Temp = +25°C, 2000MHz, 5V Supply Voltage

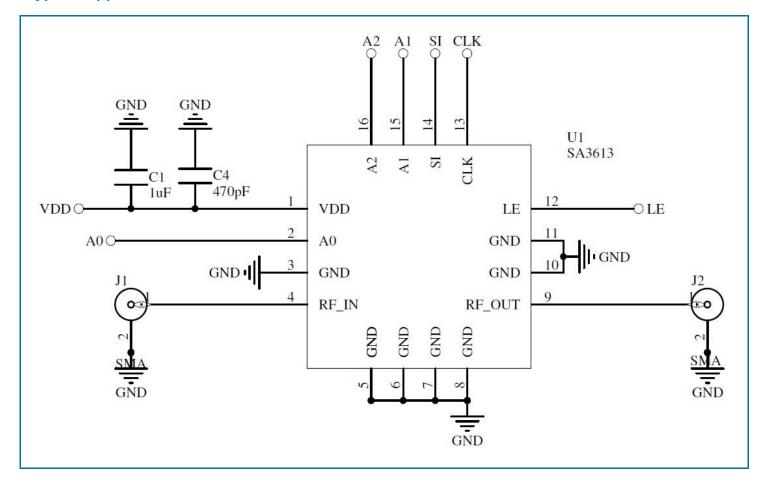

# **Typical Application Schematic**

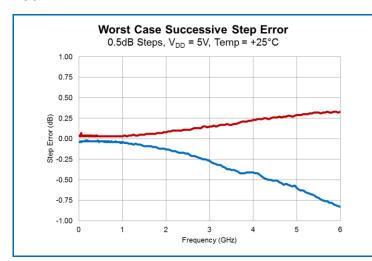

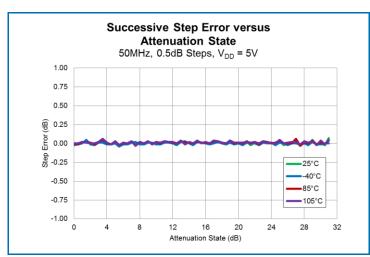

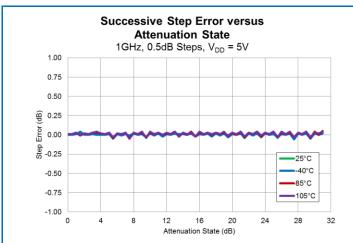

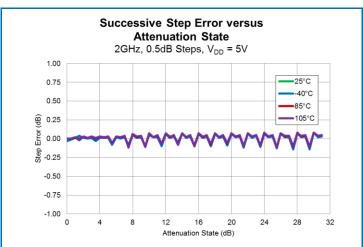

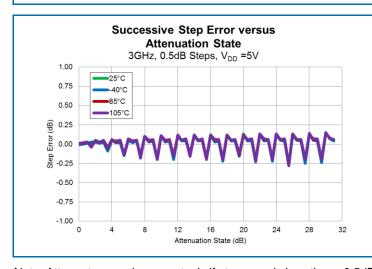

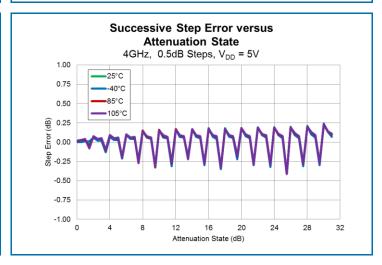

Note: Attenuator remains monotonic if step error is less than +0.5dB.

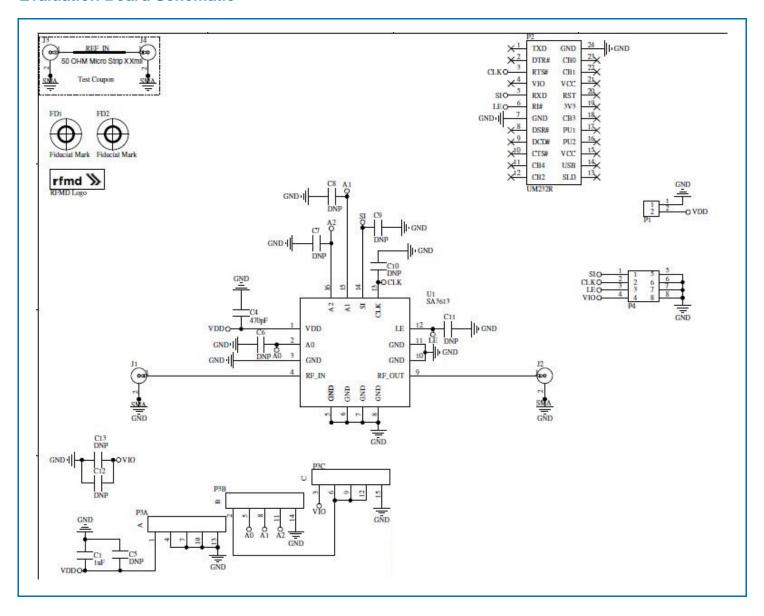

# **Evaluation Board Schematic**

# **Evaluation Board Bill of Materials (BOM)**

| Description                                | Reference Designator | Manufacturer                    | Manufacturer's P/N |

|--------------------------------------------|----------------------|---------------------------------|--------------------|

| RFSA3613-410                               |                      | Dynamic Details (DDI) Toronto   | RFSA3613-410(B)    |

| Digital Step Attenuator, 5MHz to 6000MHz   | U1                   | RFMD                            | RFSA3613SB         |

| CAP, 1µF, 10%, 25V, X7R, 1206              | C1                   | Taiyo Yuden (USA), Inc.         | CE TMK316BJ105KL-T |

| CONN, SMA, END LNCH, UNIV, HYB<br>MNT, FLT | J1-J4                | Molex                           | SD-73251-4000      |

| CONN, HDR, ST, PLRZD, 2-PIN, 0.100"        | P1                   | ITW Pancon                      | MPSS100-2-C        |

| CONN, HDR, ST, 3 x 5, 0.100", T/H          | P3                   | Samtec Inc.                     | TSW-105-07-L-T     |

| CONN, HDR, 2 x 4, RA, 0.100", T/H          | P4                   | Samtec Inc.                     | TSW-104-08-G-D-RA  |

| CONN, SKT, 24-PIN DIP, 0.600", T/H         | P2                   | Aries Electronics Inc.          | 24-6518-10         |

| MOD, USB TO SERIAL UART, SSOP-28           | M1 (See Note 1)      | Future Technology Devices Int'l | UM232R             |

| CAP, 470pF, 5%, 50V, C0G, 0402             | %, 50V, C0G, 0402 C4 |                                 | GRM1555C1H471JA01D |

| Jumpers                                    | S1-S4 (See Note 2)   | 3M Interconnect Solutions       | 929950-00          |

| DNP                                        | C5-C13               | N/A                             | N/A                |

#### Notes:

- 1. M1 should be mounted into P2 with respect to the Pin 1 alignment of M1 and P2.

- 2. Jumpers S1-S4 installed on P3.

10 of 16

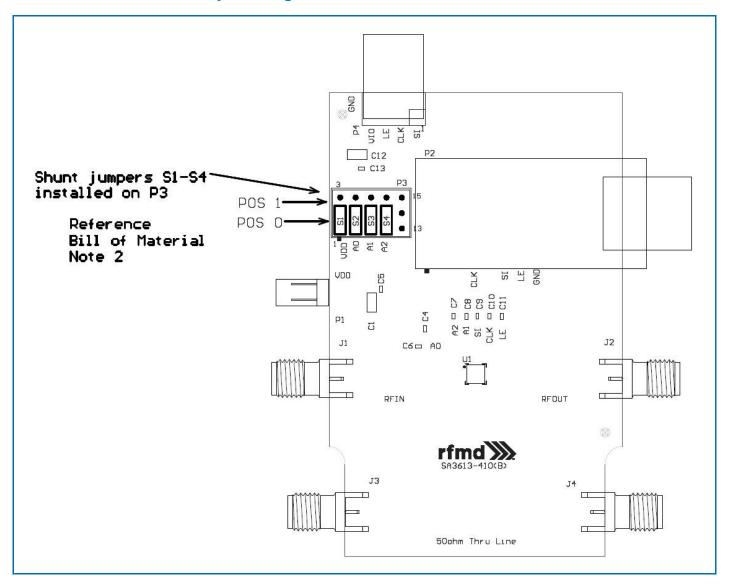

# **Evaluation Board Assembly Drawing**

#### **Evaluation Board Jumper Programming**

| Jumpers    | Connector | Signal  | Position U1 Connection |               | Comment          |

|------------|-----------|---------|------------------------|---------------|------------------|

| S1         |           | Logic   | 0                      | VDD (From P1) |                  |

| 31         |           | Voltage | 1                      | VIO (From P4) |                  |

| <b>S</b> 2 |           | AO      | 0                      | GND           | External Address |

| 32         | P3        | AO      | 1                      | U1_VDD        | External Address |

| S3         | PS        | A1      | 0                      | GND           | External Address |

| 33         |           | AI      | 1                      | U1_VDD        | External Address |

| S4         |           | 4.2     | 0                      | GND           | External Address |

| 54         |           | A2      | 1                      | U1_VDD        | External Address |

Note: Default jumper settings are **BOLD**.

#### **Evaluation Board Programming Using USB Interface**

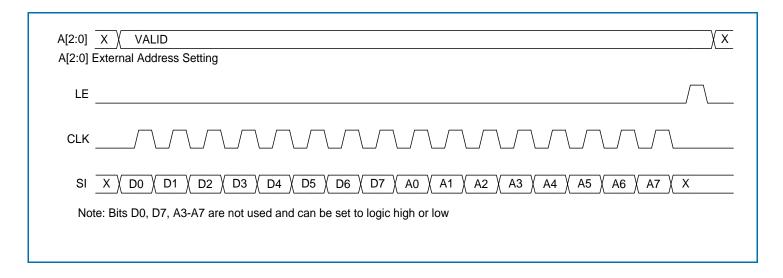

#### Serial Addressable Mode

All programming jumpers on the evaluation board are set to the default values indicated in the table. Refer to the Control Bit Generator (CBG) Software Reference Manual for detailed instructions on how to setup the software for use. Apply the supply voltage to P1. Select 'RFSA3613' from the RFMD Parts List of the CBG user interface. Set the attenuation value using the CBG user interface. The attenuator is set to the desired state and measurements can be taken. Note that the external address bits must all be set to '0' when using the USB interface as the CBG software does not have the capability to set the external address in the serial data stream at this time.

# **Evaluation Board Programming Using External Bus**

#### **Serial Addressable Mode**

This configuration allows the user to control the attenuator through the P4 connector using an external harness. Remove the USB interface board if it is currently installed on the evaluation board. Connect a user-supplied harness to the P4 connector. Note that the top row of P4 contains the serial bus signals and the bottom row is ground. Programming jumper S1 is set to '0'. External address jumpers S2 through S4 can be set to any value desired by the user. Apply the supply voltage to P1. Send the appropriate signals onto the serial bus lines in accordance with the Serial Addressable Mode Timing Diagram. The attenuator is set to the desired state and measurements can be taken.

#### **Default Power-up State**

This default attenuation state is maximum (31.5dB) when supply voltage is applied to the attenuator. The LE signal must be held to logic '0' during power-up.

# **Pin Names and Descriptions**

| Pin | Name  | Description                                                                                                                                                                                                                |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDD   | Supply Voltage                                                                                                                                                                                                             |

| 2   | A0    | A0 External Address Pin                                                                                                                                                                                                    |

| 3   | GND   | Ground Pin                                                                                                                                                                                                                 |

| 4   | RFIN  | RF Input Pin Incident RF power must enter this pin for rated thermal performance and reliability Do not apply DC power to this pin. Pin may be DC grounded externally and is grounded thru resistors internal to the part. |

| 5   | GND   | Ground Pin                                                                                                                                                                                                                 |

| 6   | GND   | Ground Pin                                                                                                                                                                                                                 |

| 7   | GND   | Ground Pin                                                                                                                                                                                                                 |

| 8   | GND   | Ground Pin                                                                                                                                                                                                                 |

| 9   | RFOUT | RF Output Pin; Do not apply DC power to this pin. Pin may be DC grounded externally and is grounded thru resistors internal to the part.                                                                                   |

| 10  | GND   | Ground Pin                                                                                                                                                                                                                 |

| 11  | GND   | Ground Pin                                                                                                                                                                                                                 |

| 12  | LE    | Latch Enable The leading edge of signal on LE causes the attenuator to change state                                                                                                                                        |

| 13  | CLK   | Serial Clock Input                                                                                                                                                                                                         |

| 14  | SI    | Serial data Input                                                                                                                                                                                                          |

| 15  | A1    | A1 External Address Pin                                                                                                                                                                                                    |

| 16  | A2    | A2 External Address Pin                                                                                                                                                                                                    |

#### **Serial Addressable Mode Attenuation Word Truth Table**

| D7 | D6 | D5 | D4 | D3 | D2 | D1<br>(LSB) | D0 | Attenuation State              |

|----|----|----|----|----|----|-------------|----|--------------------------------|

| Х  | L  | L  | L  | L  | L  | L           | Х  | 0dB / Reference Insertion Loss |

| Х  | L  | L  | L  | L  | L  | Н           | Х  | 0.5dB                          |

| Х  | L  | L  | L  | L  | Н  | L           | Х  | 1dB                            |

| Х  | L  | L  | L  | Н  | L  | L           | Х  | 2dB                            |

| Х  | L  | L  | Н  | L  | L  | L           | Х  | 4dB                            |

| Х  | L  | Н  | L  | L  | L  | L           | Х  | 8dB                            |

| Х  | Н  | L  | L  | L  | L  | L           | Х  | 16dB                           |

| Х  | Н  | Н  | Н  | Н  | Н  | Н           | Х  | 31.5dB                         |

#### **Serial Addressable Mode Address Word Truth Table**

| А7 | A6 | A5 | A4 | А3 | A2<br>(MSB) | A1 | Α0 | Address Setting |

|----|----|----|----|----|-------------|----|----|-----------------|

| Х  | Х  | Х  | Х  | Х  | L           | L  | L  | 000             |

| Х  | Х  | Х  | Х  | Х  | L           | L  | Н  | 001             |

| Х  | Х  | Х  | Х  | Х  | L           | Н  | L  | 010             |

| Х  | Х  | Х  | Х  | Х  | L           | Н  | Н  | 011             |

| Х  | Х  | Х  | Х  | Х  | Н           | L  | L  | 100             |

| Х  | Х  | Х  | Х  | Х  | Н           | L  | Н  | 101             |

| Х  | Х  | Х  | Х  | Х  | Н           | Н  | L  | 110             |

| Х  | Х  | Х  | Х  | Х  | Н           | Н  | Н  | 111             |

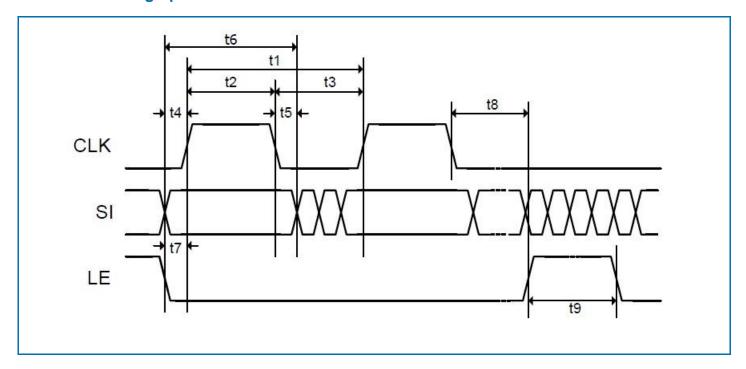

# **Serial Addressable Mode Timing Diagram**

# **Serial Bus Timing Specifications**

| Parameter | Limit | Unit    | Comment              |

|-----------|-------|---------|----------------------|

| t1        | 25    | MHz max | CLK Frequency        |

| t2        | 20    | ns min  | CLK High             |

| t3        | 20    | ns min  | CLK Low              |

| t4        | 5     | ns min  | SI to CLK Setup Time |

| t5        | 5     | ns min  | SI to CLK Hold Time  |

| t6        | 30    | ns min  | SI Valid             |

| t7        | 5     | ns min  | LE to CLK Setup Time |

| t8        | 5     | ns min  | CLK to LE Setup Time |

| t9        | 10    | ns min  | LE Pulse Width       |

#### Package Drawing (Dimensions in millimeters)

# **Branding Diagram**